Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What is the design space of the Issue Rate?

A superscalar processor is created to produce an execution rate of more than one instruction per clock cycle for a single sequential program. Superscalar processor design generally defines a set of techniques that enable the central processing unit (CPU) of a computer to obtain a throughput of more than one instruction per cycle while implementing a single sequential program.

The concept of the superscalar issue was first developed as early as 1970 (Tjaden and Flynn, 1970). It was later reformulated more precisely in the 1980s (Torng, 1982, Acosta et al, 1986).

The function of superscalar processing is the superscalar instruction issue. A higher issue rate provides rise to higher processor performance, but simultaneously, it magnifies the restrictive effects of control and data dependencies on the processor performance.

Control dependencies appear more frequently per issue in a superscalar processor, which issues multiple instructions in each cycle, than in a scalar processor. The frequent increase is roughly proportional to the issue rate of the processor.

As far as data dependencies are concerned, a higher issue rate can also strongly impede processor performance. Consider here that in a scalar processor, for instance in a pipelined processor, issue blockages due to dependencies can be avoided in most cases through the use of a parallel optimizing compiler. The compiler fills unused instruction slots, known as bubbles with separate instructions.

The second main aspect of the design space of instruction issue is the issue rate (the degree of superscalar). This rate defines the maximum number of instructions a superscalar processor can issue in a similar cycle.

A superscalar operation can be performed by issuing two, three, or more instructions in each cycle. A higher issue rate provides a higher performance possible, however, its execution is more difficult.

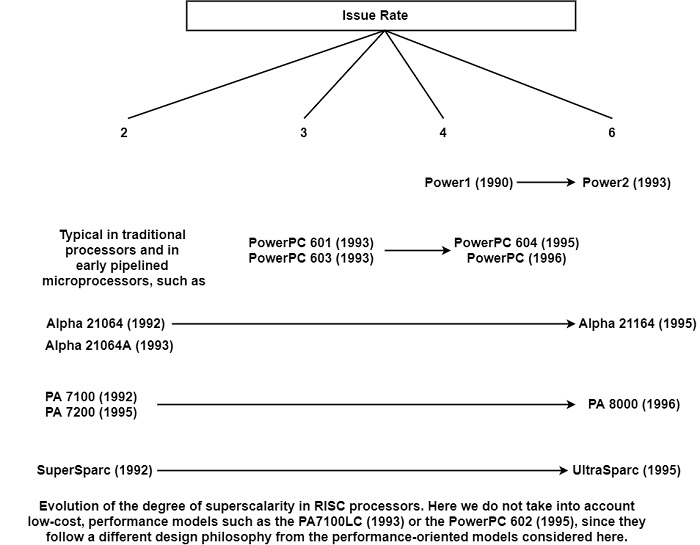

Superscalar CISC processors are generally controlled to issuing only two, or about two, instructions per cycle. In contrast, early superscalar RISC processors frequently-issued two or three instructions in each cycle. Modern RISC processors generally issue four instructions per cycle, as shown in the figure.

This diagram reveals the evolution of the issue rate sophisticated in five specific RISC lines. The first α processors (the α 21064 and α 21064A), and the first superscalar members of the HP Precision-Architecture line (PA 7100, PA 7200), were controlled to issuing two instructions per cycle.

In contrast, the first members of the PowerPC line (PowerPC 601, PowerPC 603) and the SuperSparc were capable of issuing three instructions per cycle, whereas Power1 can issue four instructions.

The Power 2 issues six instructions per cycle while executing a sequential path. However, after a guessed branch, while starting the execution of the target path, the processor issues only four instructions. Thus, Power2 is now the issue-rate leader.