Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What are the schemes for checking the availability of operands?

The availability of operands has to be checked in two scenarios such as when the operands are fetched from the register file, a scheme is needed to check whether requested contents are available in the register file. A similar scheme is needed during instruction dispatch to check whether all the operands of the instructions held in the shelving buffers are available.

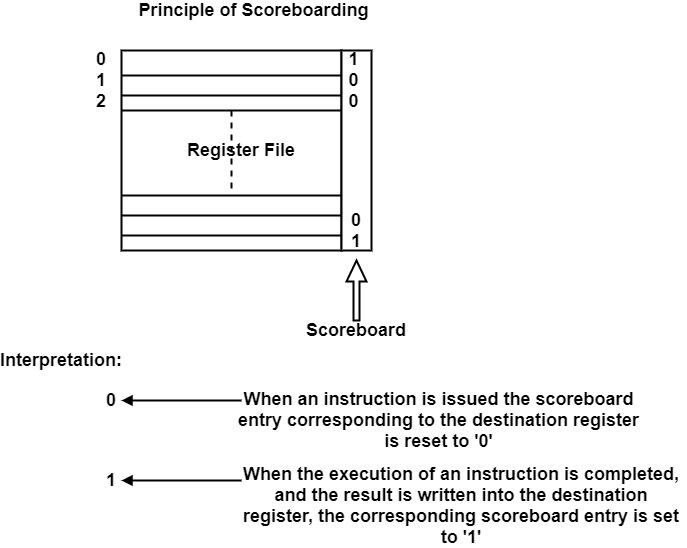

The term scoreboard was introduced in connection with CDC 6600 (1964) to denote the complex circuitry used in this processor for controlling parallel operation. The figure shows the principle of scoreboarding.

The scoreboard is a status register consisting of one-bit entries. Each of the entries may be envisaged as a one-bit extension of the corresponding register. The scoreboard bits indicate whether data in the associated register is valid, that is, available. It is usually a ‘1’ designates available data. When an instruction is issued, the scoreboard bit of the corresponding destination register is reset to 0. This indicates to all subsequent instructions requesting the contents of the register in question that its value is not yet available.

There are two basic schemes for checking the availability of operands are as follows −

In the first scheme, the reservation station does not hold any explicit status information indicating whether source operands are available or not. Thus, the availability of source operands is examined by a direct check of the scoreboard bits. This scheme is usually employed when operands are fetched during instruction dispatch.

In this scheme, decoded instructions are written into the associated reservation station, which holds the operation code (OC), the source register number, and the destination register number of the instruction issued.

In the second scheme, called the checking of the explicit status bits, the availability of source operands is explicitly denoted in the reservation stations by introducing status bits (valid bits). The status bits are then tested to see whether operands are available or not.

This scheme is generally employed if operands are fetched during instruction issues. In this case, the reservation station influences the operation code (OC), the fetched source operands, the associated valid bits, and the renaming destination register number. However, if during issue a requested operand is not yet available, the register file delivers an identifier instead of missing the operand value.

The availability of the register contents is managed by scoreboarding. During instruction issues, the scoreboard bits of the destination registers of the issued instructions are reset to ‘0’. When the EU has produced the result, the destination register is updated and the corresponding scoreboard bits are set to ‘1’. In this way, subsequently issued instructions can access the produced result value.