Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What are the basic tasks during recovery from a misprediction in computer architecture?

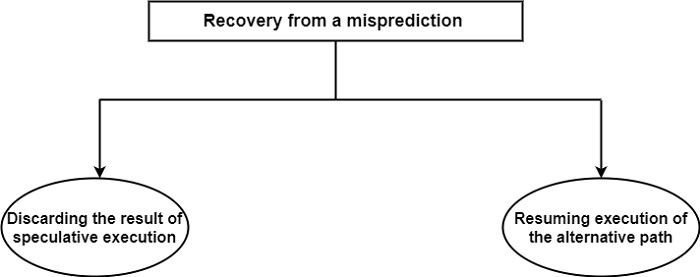

There are two basic tasks to be implemented the discard the results of the speculative execution and resume execution of the alternative, that is, the true path as shown in the figure.

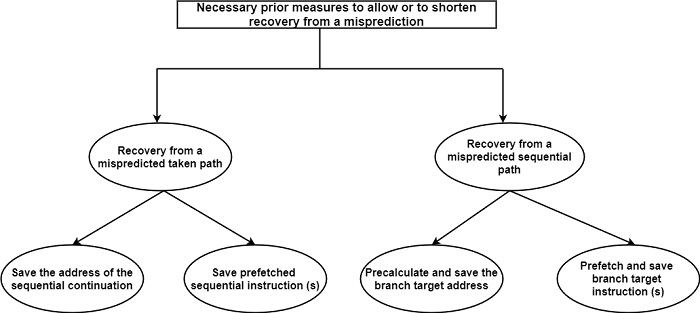

When there is higher than one pending conditional branch, the corresponding alternative path should be chosen and followed. In recovery from a mispredicted taken path, as preparation for a possible recovery from a misprediction, the processor has to store the address of the sequential preservation, before it initiates execution of the guessed taken path. The recovery phase can be minimized if previously prefetched sequential instructions are not discarded but stored for possible later use in the case of a misprediction.

The other situation is when the sequential path has been inaccurately predicted and implemented as shown in the figure. Therefore, in conjunction with the ‘not taken’ prediction, the branch target address must be pre-evaluated and stored to enable recovery.

In this case, the penalty for misprediction can be reduced by prefetching the branch target instruction for scalar processors, or some instructions in the case of superscalar processors. This needed additional buffer space and additional cache access bandwidth.

In the simplest scheme, during a prediction, only those precautionary measures are undertaken which are necessary for recovery from a misprediction. This scheme is defined as basic prior measures for recovery. The minimal provision for a misprediction covers two activities − for a ‘taken’ guess save the sequential address, for a ‘not taken’ guess, precalculate and save the branch target address. This requires two fetch address registers per speculated conditional branch to store both addresses of the possible continuations. The PowerPC 601, PowerPC 603, and PowerPC 604 use this basic scheme.

A more advanced scheme involves supplementary actions to shorten the misprediction penalty. This is often achieved by saving already prefetched sequential instructions for a ‘taken’ guess and by prefetching branch target instruction in the case of ‘not taken’ prediction. This scheme is designated as enhanced prior measures to shorten recovery. be pre-evaluated and stored to enable recovery.

The implementation of this enhanced scheme requires at least two instruction buffers with at least as many entries as instructions can be fetched in a single cycle. Examples of processors providing two instruction buffers to shorten recovery from a misprediction are the SuperSparc, Power1, Power2, and Pentium. The Nx586 provides three buffers, a sequential one and two target buffers, to cater for the two pending conditional branches allowed.

Using two instruction buffers to shorten recovery in the SuperSparc − The SuperSparc has two separate instruction buffers called the Sequential I-buffer and Target I-buffer. Both buffers can accept from the I-cache four instructions in a cycle and both have a capacity of four instructions. Since the processor employs the ‘always not taken’ prediction, in the case of an unresolved conditional branch execution always commences along the sequential path.