Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

Status register of 8257

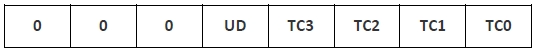

The status register is of length 8-bits wide. The processor can only read but not write and it is only selected when CS* is 0, A3-0 is 1000, and IOR* is 0.

About the present state of 8257 the information about the status is provided. The five blocks are important others are marked 0 since they are not in use.

| UD |

1 = Update in progress 0 = Update not in progress |

| TCn |

1 = TC reached for Channel n (n = 0–3) 0 = TC not yet reached for Channel n |

Fig: Interpretation of the contents of the status register

The read operation of the status register is not affected by the UD flag bit. The UD flag is made to 0 under the conditions namely

By resetting to 0 the AULD bit in the control register is disabled by the auto loaded feature.

Also after completing the UD cycle.

The bits ranging from TC3-0 to works under the following conditions.

When 8257 is made to reset

The processor reads the status register.